Table of Contents

DTL- logic families | DTL in hindi

विभिन्न प्रकार के semiconductor युक्तिओं के characteristics(अभिलक्षणों) के आधार पर digital integrated सर्किट (ICs) की रचना हुई। कई जटिल डिजिटल कार्यों को विभिन्न रूपों में विकसित किया गया और प्रत्येक रूप को एक लॉजिक परिवार का नाम दिया गया। इस लेख में हम DTL के बारे में जानेंगे जो बाइपोलर लॉजिक परिवारों का एक सदस्य है। Click here to Read this article in English

Diode Transistor Logic

DTL परिपथ RTL परिपथों की तुलना में अधिक जटिल होते हैं परन्तु इसकी अधिक FAN OUT क्षमता एवं सुधरे हुए नॉइज़ मार्जिन के कारण इस लॉजिक ने RTL को प्रतिस्थापित (replace) कर दिया है। DTL का मुख्य दोष इसकी धीमी गति है एवं इसी दोष के कारण ही DTL में मॉडिफिकेशन किये गए तथा TTL-Transistor Transistor logic का विकास हुआ। आज TTL एक अत्यंत लोकप्रिय एवं शक्तिशाली लॉजिक परिवार है तथा SSI एवं MSI में इसकी क्रिया प्रणाली अत्यंत विश्ववसनीय है। TTL-Transistor Transistor logic की श्रेष्ठता को समझने के लिए हमे पहले DTL को समझना होगाT।

प्रारंभ में इनपुट डायोड एवं एक ट्रांजिस्टर इन्वेर्टर का प्रयोग कर D.T.L. परिपथ बनाया गया जिसे बाद में integrated circuit (ICs) के रूप में विकसित किया गया।

फोटो में एक 3-इनपुट DTL NAND gate दिखाया गया है। DTL प्रणाली का बेसिक gate एक NAND gate है। इनपुट डायोड DA, DB, DC में प्रतिरोध R के माध्यम से चालन होता है। डायोड में चालन केवल तभी होता होता है जब इनपुट LOW state में हो। इनपुट हाई होने पर डायोड Non-conducting state में रहते हैं। अतः यदि कोई एक इनपुट LOW state में है तब इस इनपुट से संयोजित डायोड फारवर्ड बायस में होगा तथा इसमें चालन होगा। बिंदु P पर उत्पन्न वोल्टेज ट्रांजिस्टर T को कट ऑफ में रखती है अतः परिपथ की आउटपुट Vcc के बराबर अर्थात HIGH होगी।

इसके विपरीत यदि तीनों इनपुट HIGH state में हैं तब इनपुट डायोड DA, DB एवं DC कट ऑफ हो जायेंगे तथा सप्लाई Vcc से प्रतिरोध R के द्वारा धारा प्रवाह होगी जो ट्रांजिस्टर को सचुरेशन में ले जाएगी तथा परिपथ की आउटपुट LOW हो जाएगी। आउटपुट का यह LOW स्तर VCE(sat) के बराबर होगा।

DTL AND तथा OR गेट

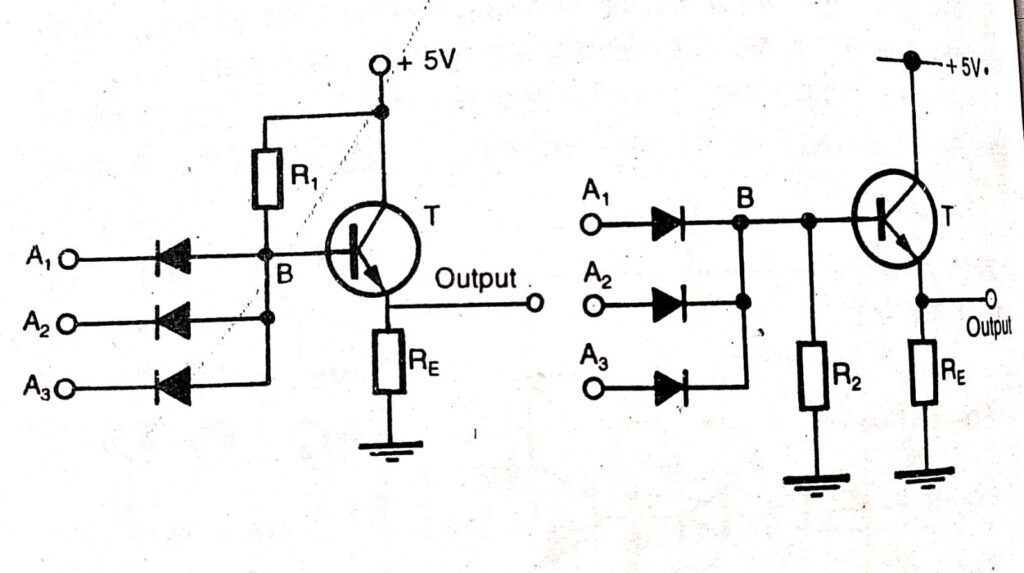

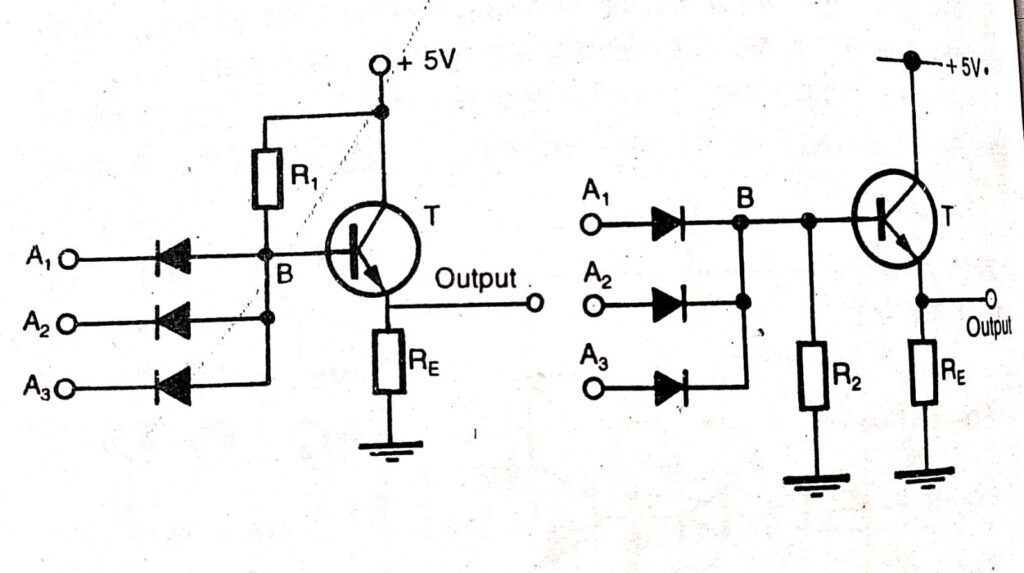

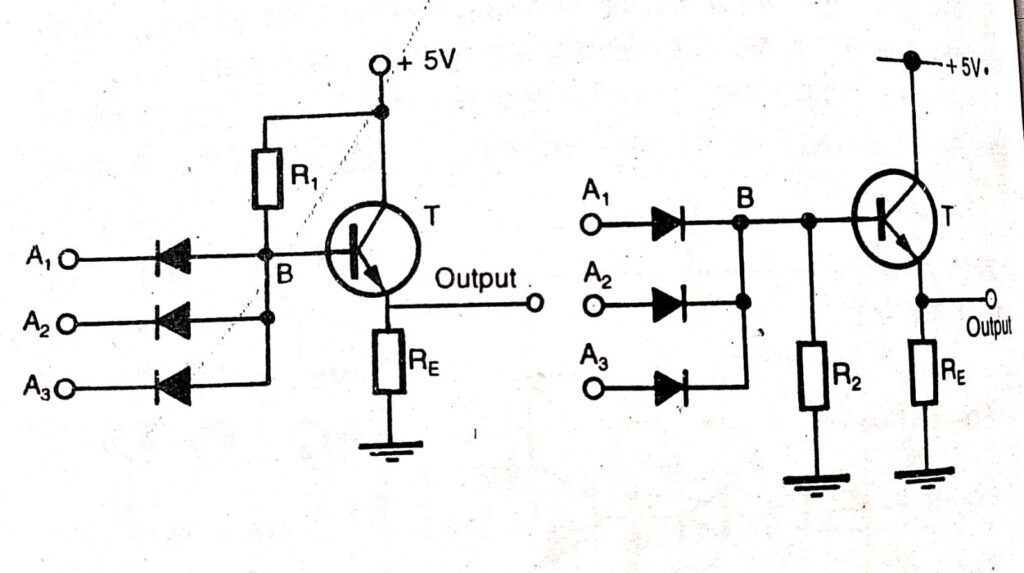

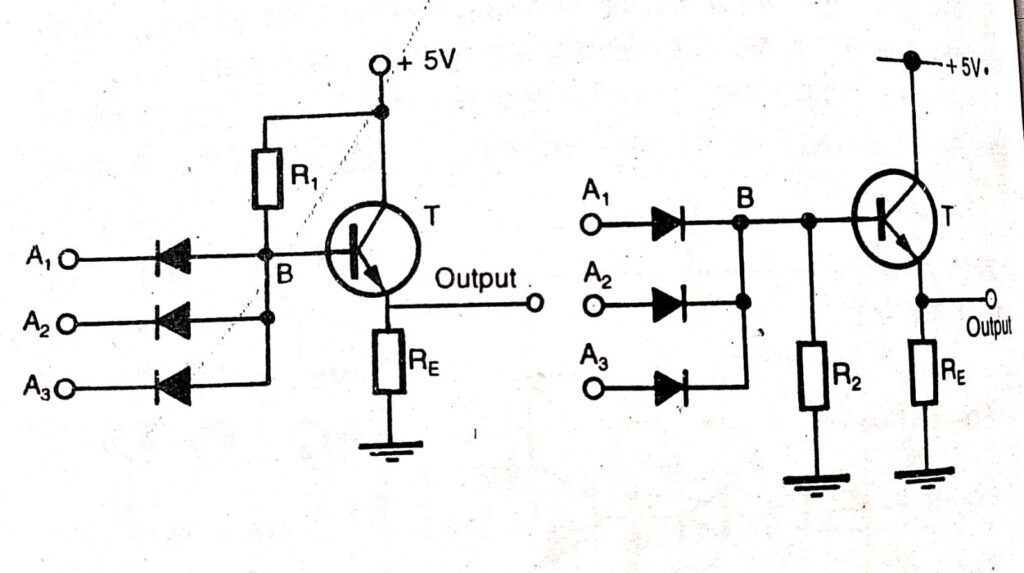

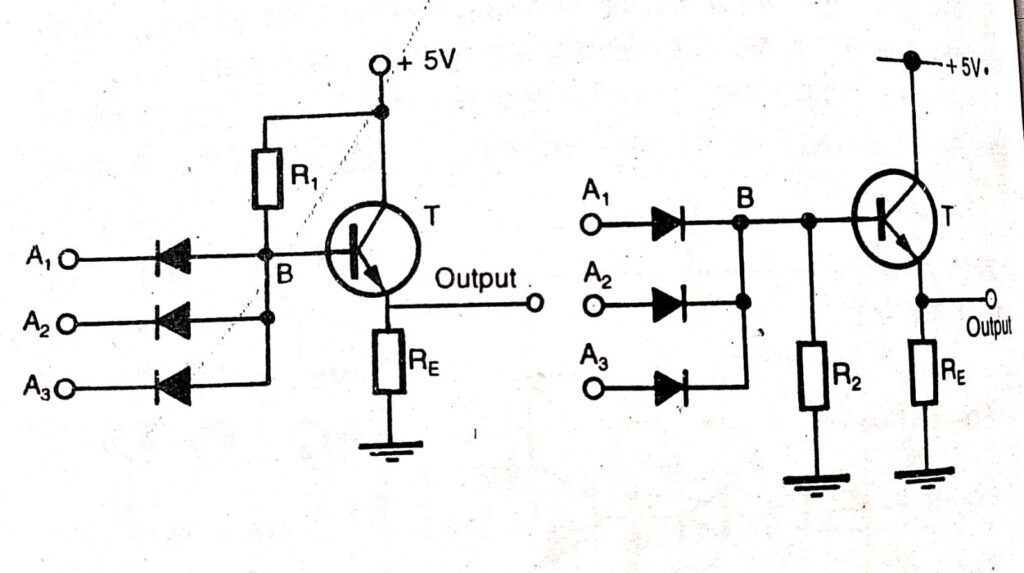

नीचे फोटो में बायीं तरफ DTL AND gate तथा फोटो में दायीं तरफ DTL OR gate दिखाया गया है। दोनों परिपथों में लॉजिक state 1 तथा 0 के लिए क्रमशः पॉजिटिव लॉजिक +5V तथा 0V माने गए हैं।

DTL AND परिपथ (बायीं तरफ) में जब कोई भी इनपुट(A1, A2 अथवा A3) निम्न लॉजिक (0) पर होती है तब उस इनपुट से संयोजित(connected) डायोड फॉरवर्ड बायस में होता है तब ट्रांजिस्टर T कट ऑफ में आ जाता है तथा आउटपुट LOW (लॉजिक0) होती है। यदि सभी इनपुट लॉजिक 1(+5V) पर होती हैं तब किसी भी डायोड में चालन नही होता है तथा ट्रांजिस्टर T में अत्याधिक चालन होता है। ट्रांजिस्टर सेचुरेट हो जाता है एवं आउटपुट HIGH (लॉजिक 1) होती है।

फोटो में दायीं तरफ DTL OR gate दिखाया गया है। यदि कोई भी इनपुट लॉजिक 1 (+5V) पर होती है तब उस से संयोजित डायोड में चालन होता है तथा ट्रांजिस्टर का base(बिंदु B) +5V पर होता है। ट्रांजिस्टर में अत्याधिक चालन के कारण यह सेचुरेट हो जाता है तथा आउटपुट HIGH (लॉजिक 1) हो जाती है। यदि सभी इनपुट ग्राउंड स्तर (लॉजिक 0) पर हैं तब कोई भी डायोड कंडक्ट नहीं करेगा तथा बिंदु B पर वोल्टेज 0 होगी। परिणाम स्वरुप ट्रांजिस्टर कट ऑफ हो जायेगा तथा आउटपुट LOW (लॉजिक 0) होगी।

D.T.L. के पैरामीटर्स

- FAN Out – 8

- Noise margin- 0.7 volts

- Propagation Delay- 30n sec

- Power Dissipation -60mW

- Power Supply Voltage(Vcc)- +5 V

DTL के गुण एवं दोष

DTL सर्किट में RTL सर्किट के तुलना में अधिक तीव्र गति से स्विचिंग होती है क्युकी सिग्नल का ट्रांजिस्टर में प्रवाह फॉरवर्ड बायस्ड डायोड के निम्न (Low) प्रतिरोध द्वारा होता है। DTL सर्किट में संयोजित गेट्स के 1 state में होने के कारण इनपुट प्रतिबाधा उच्च होती है अतः FAN OUT की संख्या अधिक(8) प्राप्त की जा सकती है। DTL सर्किट्स में प्रतिरोध तथा कैपेसिटर के स्थान पर डायोड के प्रयोग से ये ICs के रूप में सस्ते होते हैं क्युकी ICs पर डायोड फेब्रिकेशन, प्रतिरोध एवं कैपेसिटर की तुलना में सरल है। DTL सर्किट्स में power loss निम्न होता है।

D.T.L. सर्किट्स के मुख्य दोष इनका poor noise margin तथा निम्न प्रचालन गति है।

ये भी पढ़ें

- Logic Families-Resistor Transistor Logic | RTL

- रिले | Relay in hindi | Relay wiring diagram in hindi

- What is a busbar in hindi

- P&id symbols in hindi

- Integrated Circuit in hindi | ICs क्या होती हैं ?

- Logic gates in hindi